来源:小编 更新:2024-12-03 09:23:58

用手机看

随着电子技术的飞速发展,FPGA(现场可编程门阵列)在嵌入式系统设计中的应用越来越广泛。VHDL(Very High Speed Integrated Circuit Hardware Description Language,非常高速集成电路硬件描述语言)作为一种硬件描述语言,被广泛应用于FPGA设计中。本文将探讨如何使用VHDL进行游戏设计,并通过实际案例展示VHDL在游戏开发中的应用。

VHDL是一种硬件描述语言,用于描述数字电路的行为、结构和数据流。它具有以下特点:

行为描述:VHDL可以描述电路的行为,如逻辑门、触发器等。

结构描述:VHDL可以描述电路的结构,如模块、子模块等。

数据流描述:VHDL可以描述电路的数据流,如信号、总线等。

可移植性:VHDL代码可以在不同的FPGA开发平台上运行。

使用VHDL进行游戏设计,通常需要以下步骤:

需求分析:明确游戏的目标、规则和功能。

模块划分:将游戏功能划分为多个模块,如显示模块、输入模块、游戏逻辑模块等。

模块设计:使用VHDL语言设计各个模块,实现游戏功能。

模块集成:将各个模块集成到一起,形成一个完整的游戏系统。

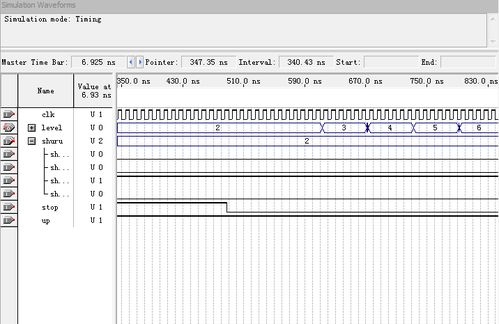

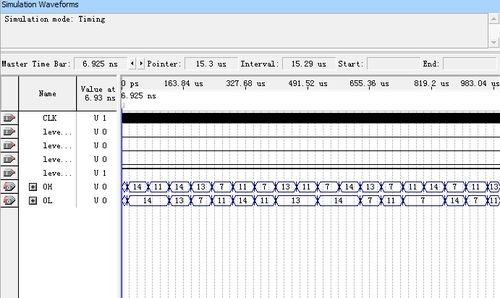

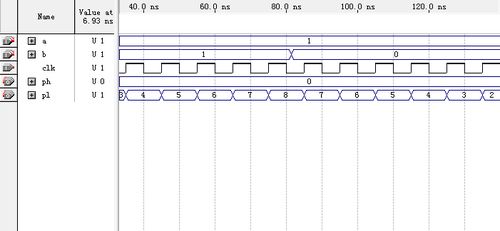

仿真测试:使用仿真工具对游戏系统进行测试,确保功能正确。

硬件实现:将VHDL代码下载到FPGA开发板上,进行硬件实现。

以下是一个使用VHDL实现的贪吃蛇游戏案例,展示了VHDL在游戏开发中的应用。

1. 游戏需求分析

贪吃蛇游戏是一款经典的街机游戏,玩家控制一条蛇在屏幕上移动,吃掉食物,使蛇变长。游戏规则如下:

玩家使用键盘控制蛇的移动方向。

蛇吃到食物后变长,否则长度不变。

当蛇撞到墙壁或自身时,游戏结束。

2. 模块划分

根据游戏需求,将贪吃蛇游戏划分为以下模块:

显示模块:负责显示游戏画面。

输入模块:负责读取玩家的按键输入。

游戏逻辑模块:负责处理游戏逻辑,如蛇的移动、食物的产生等。

3. 模块设计

以下是一个简单的贪吃蛇游戏模块设计示例:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity snake_game is

Port (

clk : in STD_LOGIC;

reset : in STD_LOGIC;

direction : in STD_LOGIC_VECTOR(1 downto 0);

food : out STD_LOGIC_VECTOR(5 downto 0);

snake : out STD_LOGIC_VECTOR(5 downto 0);

game_over : out STD_LOGIC

);

end snake_game;

architecture Behavioral of snake_game is

signal snake_pos : STD_LOGIC_VECTOR(5 downto 0) := (others => '0');

signal food_pos : STD_LOGIC_VECTOR(5 downto 0) := (others => '0');

signal game_over_flag : STD_LOGIC := '0';

begin

process(clk, reset)

begin

if reset = '1' then

snake_pos '0');

food_pos '0');

game_over_flag 4. 模块集成与仿真测试

将各个模块集成到一起,形成一个完整的游戏系统。使用仿真工具对游戏系统进行测试,确保功能正确。

5. 硬件实现

将VHDL代码下载到FPGA开发板上,进行硬件实现。通过FPGA开发板上的显示屏和键盘